阻抗PCB疊層設計是硬件工程師和PCB工程師必備技能之一,Layout工程師會依據疊層設計進行Layout設計,包括線寬、線距、差分走線等設置 。特性阻抗匹配是指在信號能量傳輸時,要求負載阻抗要和傳輸線的特征阻抗相等,此時的傳輸不會產生反射,這表明所有能量都被負載吸收了,反之則在傳輸中有能量損失,故掌握特性阻抗的計算也很重要。

1.阻抗分類

(1)單端阻抗(Single?Ended?Impedance):單根信號線測得的阻抗(常用);

(2)差分阻抗(Differential?Impedance):差分驅動時在兩條等寬等距的傳輸線測得的阻抗(常用);

(3)共面阻抗(Coplanar?Impedance):信號線在其周圍GND/VCC之間傳輸時所測試到得阻抗(不常用)。

2.阻抗影響因素

(1)正比因素:線路層與接地層間介質厚度H1/H2/H3、相鄰線路與線路間的距離S;

(2)反比因素:介電常數Er、線底寬度W1、線面寬度W2、銅厚T、基材阻焊厚度C1、線面阻焊厚度C2、線間阻焊厚度C3、阻焊介電常數CEr。

故關系式可以理解為Z=HS/Er*W*T*C*CEr。

3.疊層設計

(1)確定基材:根據產品的使用環境要求和板廠備料情況,選擇合適的PCB板材(提取Er),常見的有:Tg=150的生益S1411 150板材,Tg=180的臺耀TU-768板材。

(2)確定板厚:根據產品要求或者設備結構要求,確定線路板的成品板厚,常見的有:0.8mm、1.0mm、1.2mm、1.6mm、2.0mm,誤差一般為10%。

(3)確定板層數:根據元器件的密集程度以及信號復雜程度,確定線路板的布線層數,常見的有:單層、雙層、4層、6層、8層及以上。

(4)確定布線層布局:根據產品的特性進行布線層的布局,比如4層板有:Top(Singel)-L2(GND)-L3(GND/VCC)-Bottom(Singel),此方式適用于大部分的電子設備,SI性能較好;Top(GND)-L2(Singel/VCC)-L3(Singel/VCC)-Bottom(GND),此方式適用于射頻類電子設備,EMI性能較好。

(5)確定特性阻抗值:根據產品的所有信號類型及特性,確定所有需要管控特性阻抗的阻抗值,常見的有:單端特性阻抗=45/50/55/60歐姆,差分特性阻抗=85/90/100歐姆。

(6)設計疊層參數:依據所需阻抗值,使用Polar-Si9000軟件設計管控信號線的各層線寬、線距、層間介質厚度、銅厚、阻焊厚度等參數設計合理的疊層參數,一般線寬選擇≥4mil、線距選擇≥5mil,信號層和參考層的介質厚度在2.5mil≤H≤6mil,內層銅厚=1oz,外層銅厚+Plating=0.5oz。

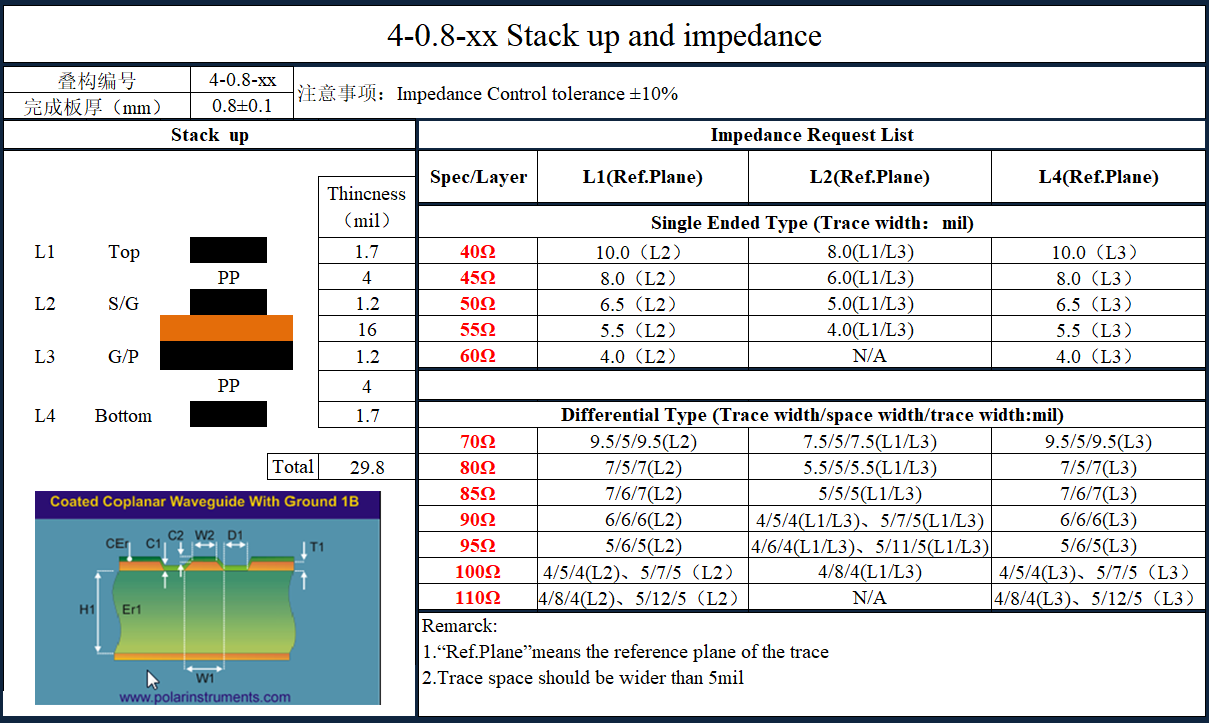

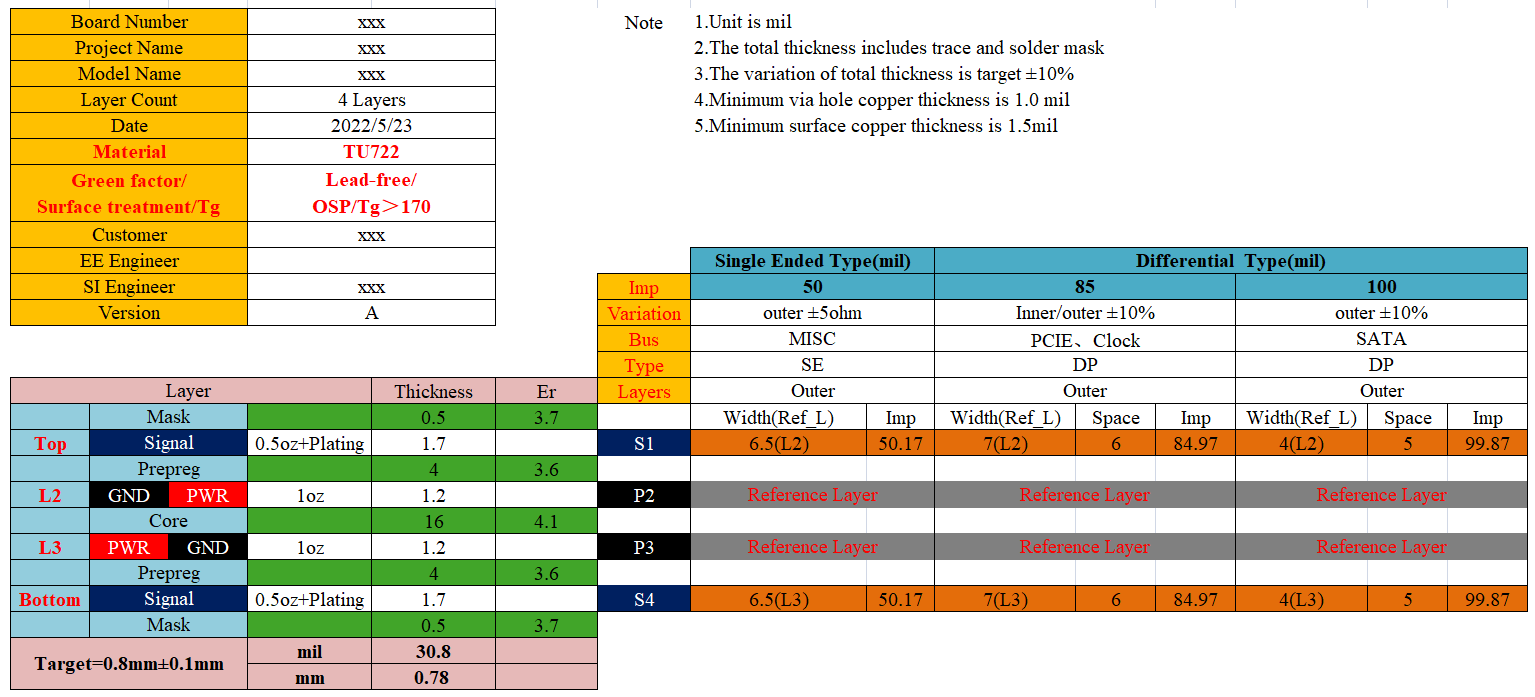

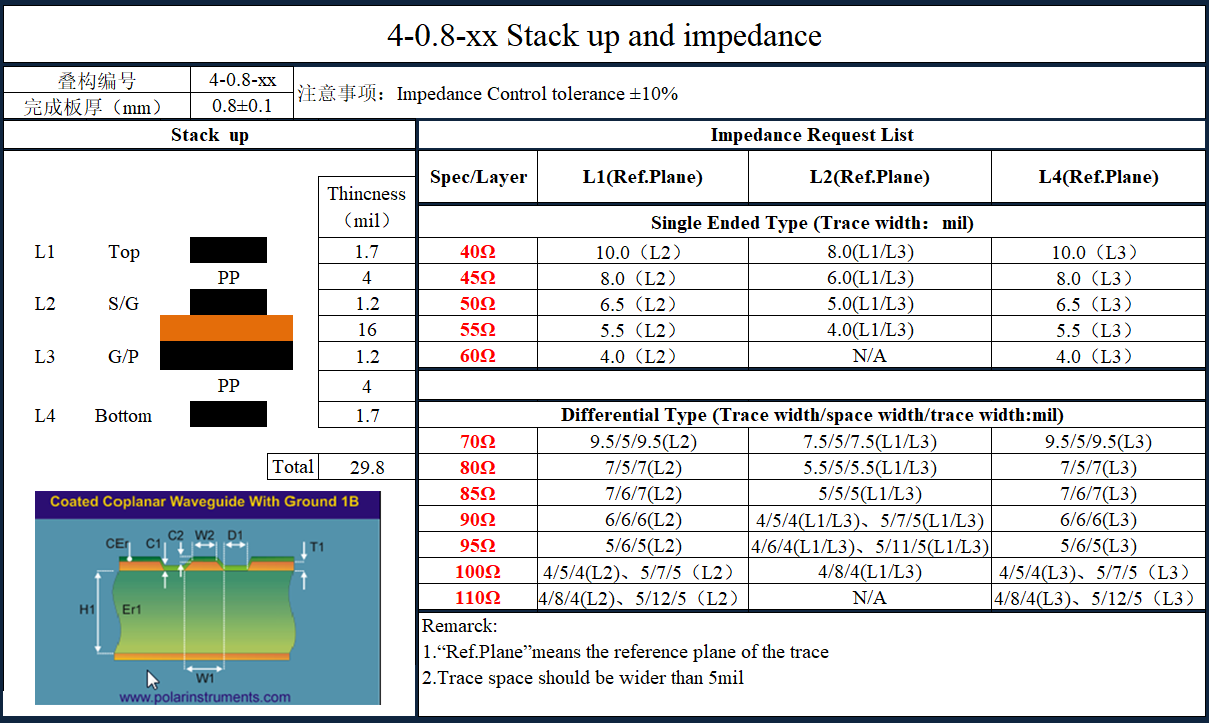

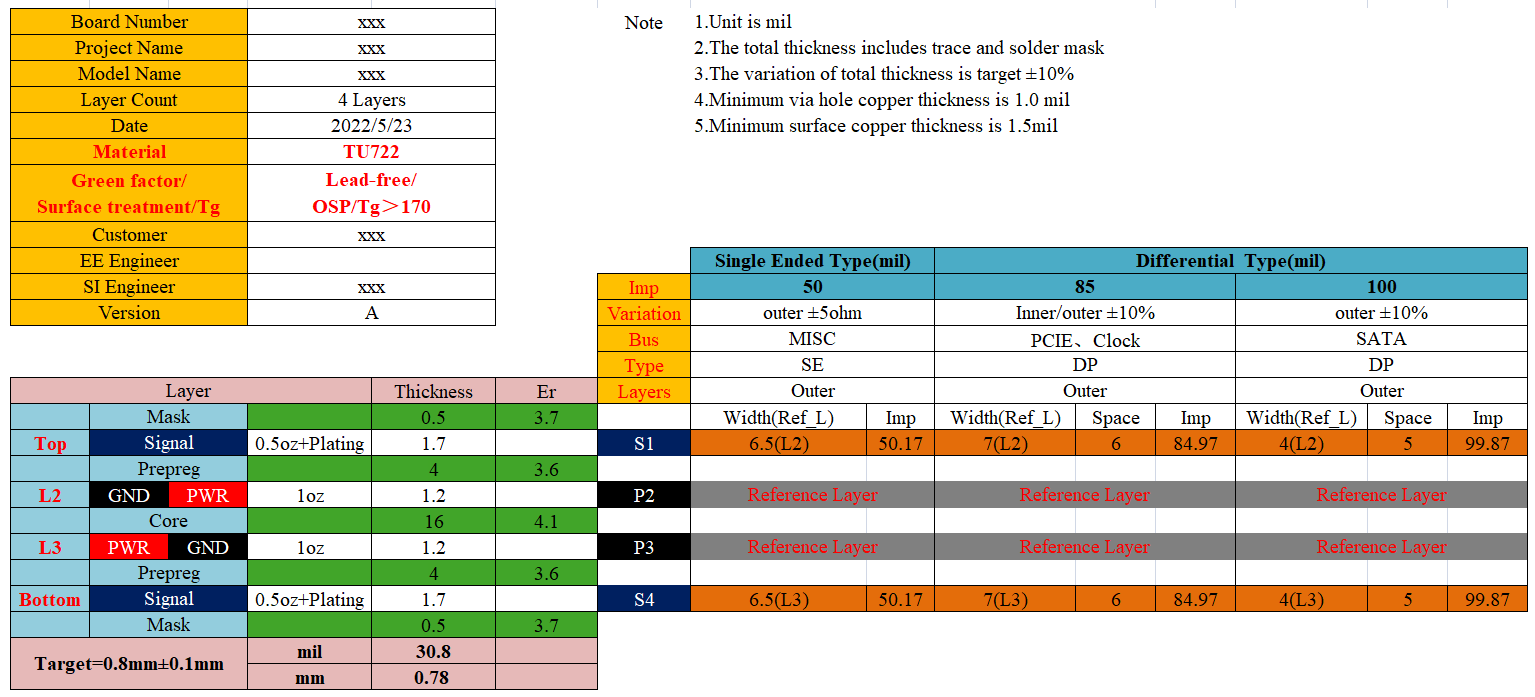

(7)設計疊層表:設計疊層表以供板廠確認,板廠會進行微調及確認,得到最終的疊構表。如下圖1所示為通用型疊層表,圖2為專用型疊層表。

注:通用型疊層表:需要額外提供疊層信息給板廠,并將表格中不需要管控特性阻抗部分的信息隱藏起來,只留需要管控的部分。

專用型疊層表:疊層信息比較全面,無需額外提供資料,管控的特性阻抗也提取出來。

圖1 4層板通用型疊層表

圖2 4層板專用型疊層表

4.特性阻抗計算

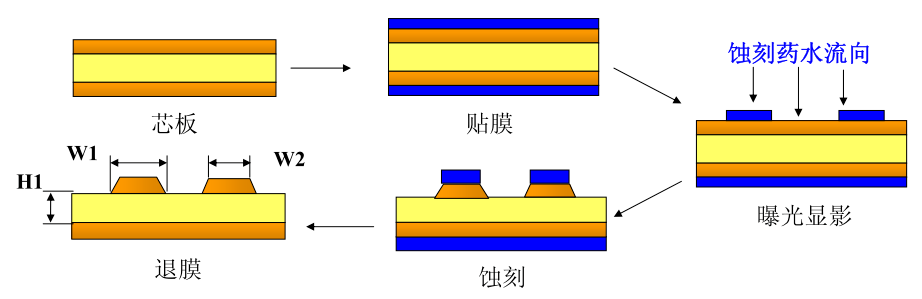

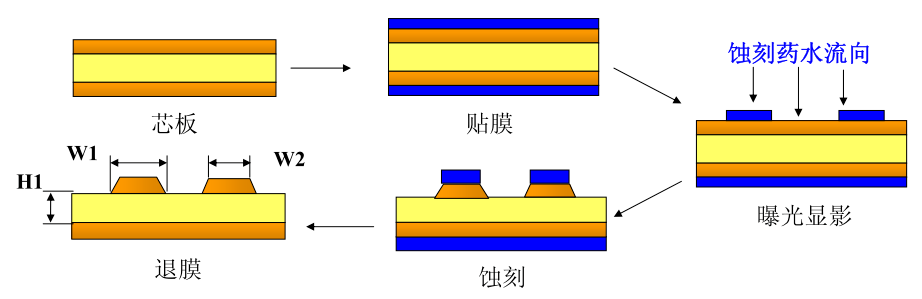

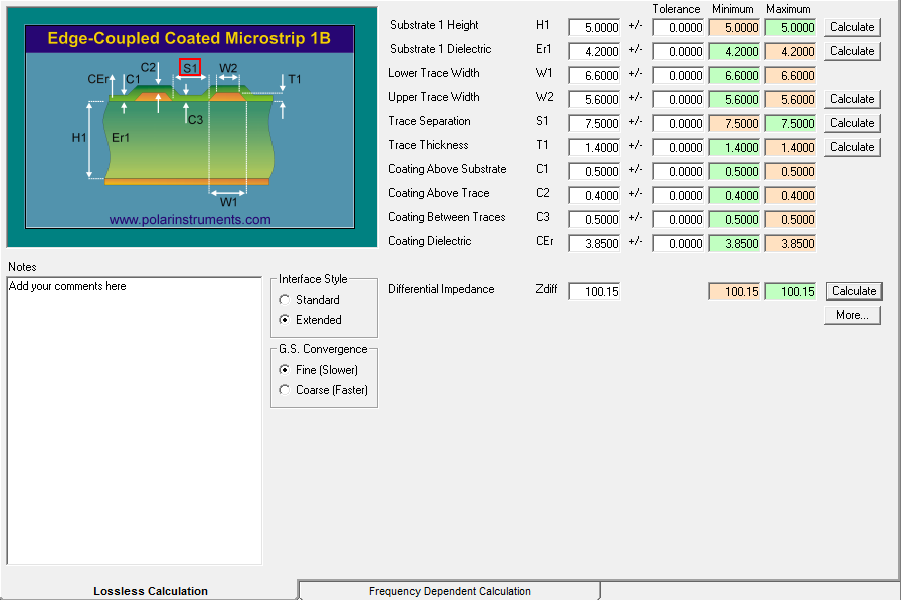

Polar-Si9000軟件是大多數工程師首選的阻抗特性計算軟件,該軟件共提供了93種阻抗計算模式,完全滿足大部分PCB板阻抗計算要求,且計算結果的準確度和精度較高。當選擇不同的阻抗計算模式時,其計算公式的因子略微不同,其基本因素就是上述提到的H、S、Er、W1、W2、C1、C2、C3、CEr。線寬分為W1和W2的原因見下圖3制作流程。生產中蝕刻藥水對至上而下銅表面進行腐蝕,因此蝕刻出來的線寬會呈現出梯形,W1與W2的差值與銅厚相關,其差值一般為0.3-1.6mil之間,具體如下:

(1)內層:銅厚T=1oz時,W1=W2+0.5mil;銅厚T=2oz時,W1=W2+1.2mil ;

(2)外層:銅厚T=1oz時,W1=W2+1.0mil;銅厚T=2oz時,W1=W2+1.6mil ;;

(3)與板廠確認W1和W2的關系。

圖3 制作流程

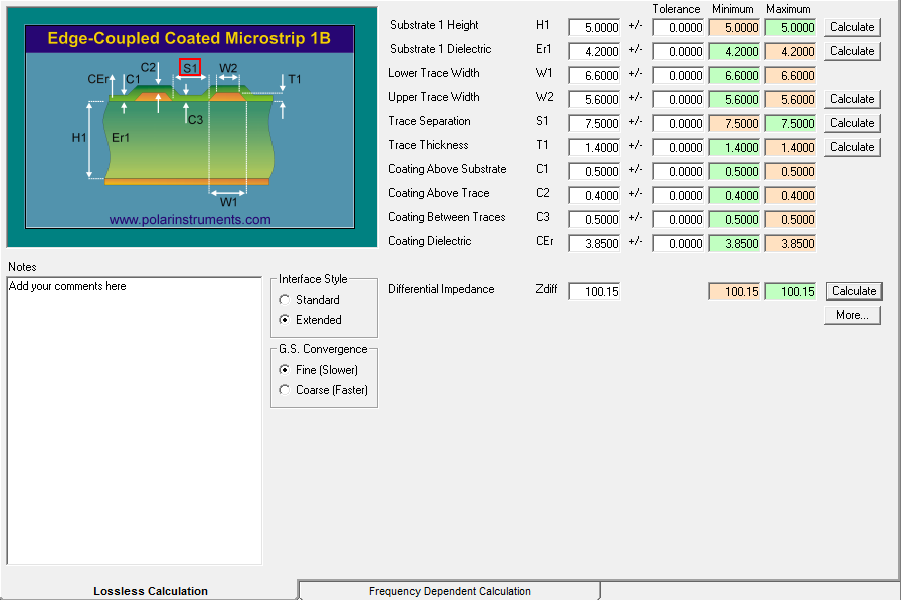

如下圖4所示是Polar-Si9000的 Edge-Coupled Coated Microstrip 1B模式,現可確定的參數有(板材、油墨、銅厚確定后):Er1=4.2、T1=1.4mil、C1=0.5mil、C2=0.4mil、C3=0.5mil、CEr=3.85;H1設定為5mil。剩下的可調參數為(差分的線寬和線距):W1、W2、S1。此時可以嘗試著先定S1,再定W1和W2,或者先定W1和W2,再定S1都可以。比如先定S1=7.5mil,然后慢慢的調整W1和W2數值,直至特性阻抗值達到預計值(Z=100oz),此時W1=6.6,W2=5.6。此時就算完成了該層100歐姆差分特性阻抗的計算,如果該層或者其它層還有特性阻抗要求,還需要按此方式去再計算,直至把整個PCB設計的特性阻抗都計算出來。

圖4 差分特性阻抗100歐姆計算